随着集成电路进入纳米尺度,电路特征尺寸已靠近物理下限,光刻可制造技术已经成为集成电路设计的关键难题之一。在先进工艺节点,已经提出了超紫外线刻蚀(EUV),电子束刻蚀(EBL),定向自组装光刻(Directed self-assembly, DSA)以及多重图案光刻(Multiple patterning lithography,MPL)等先进光刻技术。超紫外线刻蚀技术和电子束刻蚀技术尚无法实现芯片的量产。定向自组装光刻需要借助引导模板来生产目标图案,为了生产复杂的芯片版图,需要用到复杂的引导模板,而复杂的引导模板会严重降低芯片的可制造性和成品率。虽然多重图案光刻能够显著增强曝光能力,但随着集成电路特征尺寸进一步缩小到14纳米以下,版图图案更加密集,已很难将原始版图图案分解到多张掩膜版上且不产生图案冲突。

传统求解多重图案和电子束混合工艺版图图案分解问题,采用的是直接两阶段方法,又称为多重图案分解后处理方法,该方法的优势在于可重用已有经典的多重图案版图分解方法。但是,由于多重图案缝合点数目和电子束使用的优化分别是在两个阶段内独立地进行,因而并不能得到较优的求解质量。实验室曾璇教授课题组提出了电子束和多重图案混合工艺版图图案分解方法,能够同时优化电子束使用面积和多重图案光刻的缝合点数目。针对电子束和双重图案混合工艺,提出一种基于primal-dual的方法,该方法能够在合理的时间内获得优于传统两阶段方法的求解结果,可用于解决大规模版图的图案分解问题。针对电子束和多重图案混合工艺,提出一种随机初始化的局部搜索方法,基于primal-dual的方法,进行迭代求解,寻找全局最优解,并行程度高。

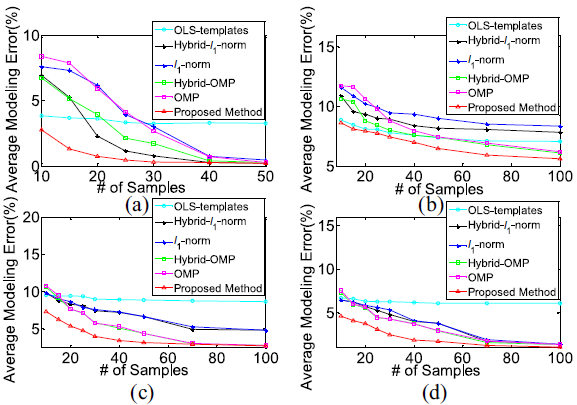

这一成果“Efficient Hybrid Performance Modeling for Analog Circuits Using Hierarchical Shrinkage Priors”发表在集成电路自动化设计领域最具影响力的国际期刊IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems。