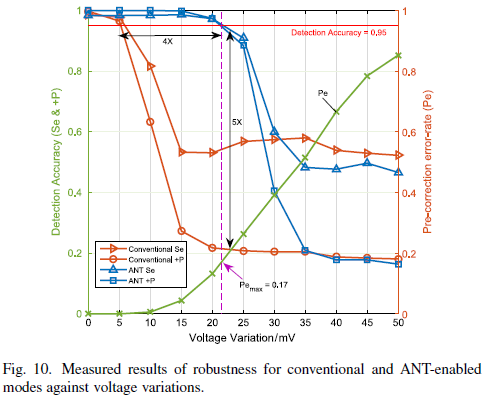

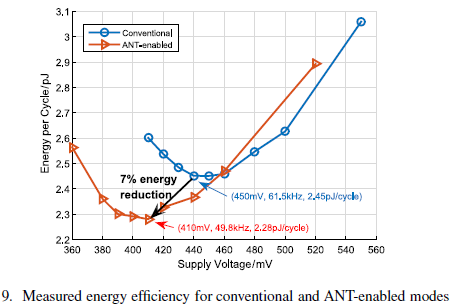

实验室曾晓洋教授课题组在亚阈值可容错ECG处理器研究中,提出了基于加权均值双边预测的ANT(Algorithmic Noise Tolerance)技术和两级异构容错方案。提出的ANT方法通过在信号的预测窗口中提升可信样本的权重,而降低未验证样本的权重,从而提高估计准确度。基于所提出的容错技术,设计实现了一款低电压、可容错的心电信号处理芯片。该ECG 信号处理芯片共有三级流水线,第一级是小波滤波器组,第二级和第三级是 GLRT 模块。容错电路的第一级采用基于影子寄存器技术的时序检测链,来监控电路的时序错误,容错电路的第二级采用基于比较器的检错机制,两级检错电路都使用了一个预测长度为 4 的加权均值双边预测估计器, 估计器的系数通过实验确定,并且为了节省硬件面积和功耗开销,选择 m/8 或者 n/16 作为系数, m 和 n 为整数,因为这些系数可以通过移位和加法实现。流片结果表明,该心电信号处理电路的ANT模块只占主干电路5%的面积,可在电压过缩放条件下容纳17%的错误率,实现低电压工作(可低至0.41V),能效(energy/cycle)可达到2.28pJ。

成果相关论文“An Area-Efficient Error-Resilient Ultralow-Power Subthreshold ECG Processor”发表在IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II-EXPRESS BRIEFS上。