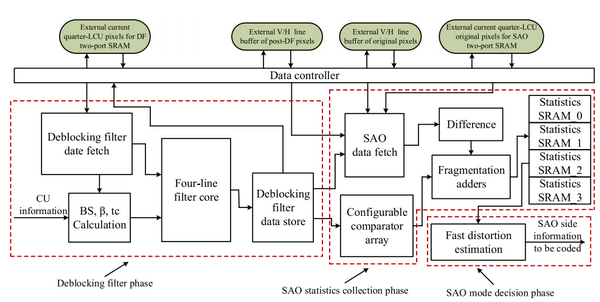

随着视频分辨率从高清(1920x1080像素)迈向4K(3840x2160)以及虚拟现实VR应用(分辨率>16K),使得视频编码芯片需要处理海量的图像数据,芯片设计面临严峻的外存带宽瓶颈,同时HEVC/H.265视频编码标准又将芯片设计复杂度推向更高级别。面对上述芯片带宽与计算性能问题,实验室曾晓洋教授课题组针对HEVC/H.265视频编码器中的De-blocking Filter和SAO模块,提出了数据复用、硬件融合的设计理念,将两个算法模块的流水线进行合并,形成新型的统一计算流水线架构(如图所示)。上述设计方案消除了De-blocking Filter和SAO之间对外存IO带宽的需求,并节省25%的片上内存。在流水线内部设计上,在De-blocking Filter计算中采用了创新的交叉存储的映射方式,使得垂直和水平边滤波时都能高效地从存储器中读取数据,同时在SAO模式判决部分采用了基于加法器操作求得相应各个模式的简化算法,最终实现数据吞吐率是同类设计的3-7倍,可满足8K@40fps的视频编码需求。成果“A Combined Deblocking Filter and SAO Hardware Architecture for HEVC”发表在IEEE TRANSACTIONS ON MULTIMEDIA上。