Delta-Sigma模/数转换器是一种用于实现高精度模/数转换的重要体系结构,Delta-Sigma调制器是它的核心组成部分。随着CMOS工艺技术特征尺寸的不断缩小,电源电压日益降低,输入前馈式Delta-Sigma调制器因内部较小的电压摆幅而逐渐成为新的研究热点,它具有功耗低、谐波失真小等等优点。然而,在电路实现时它却暴露出非常严重的时序约束问题,从2001年该调制器结构首次被提出以来,这个问题至今仍没有得到较好的解决。

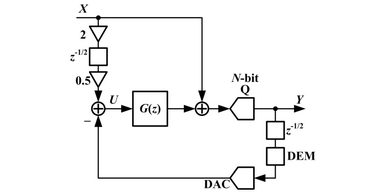

为了解决时序约束问题,实验室李巍教授课题组提出了一种通用的倍压采样/电荷再分配输入前馈式Delta-Sigma调制器结构(DVS/CR IFF DSM,如图1所示)和它的实现电路。在系统级,通过等价变换在环路滤波器的输入路径和反馈路径均引入“半周期延时”,并且,让输入路径的“半周期延时”与反馈路径的模拟求和、量化及动态元件匹配操作共用一个时钟相,从而使时序约束得到了极大宽松;在电路级,采用DVS/CR技术实现了输入路径的“半周期延时”,同时,通过共享二次采样电容使调制器的反馈路径保持不变,从而避免了量化噪声折叠。理论分析表明,DVS/CR IFF DSM的失配噪声和电路噪声都比传统调制器的低;电路仿真显示,DVS/CR IFF DSM的综合性能FOMS达到168.2 dB,已经十分接近国际上同类调制器的最高水平。总而言之,DVS/CR IFF DSM既解决了时序问题又拥有良好的性能,可以广泛应用于低压、高精度的模/数转换,具体应用例如:测量仪器、通信系统、数据采集、医学成像等等。

目前,代表该研究成果的论文“An Input-Feedforward Delta-Sigma Modulator With Relaxed Timing Constraints” DOI: 10.1109/TCSII.2017.2689246已发表在IEEE Transactions on Circuits and Systems II: Express Briefs。