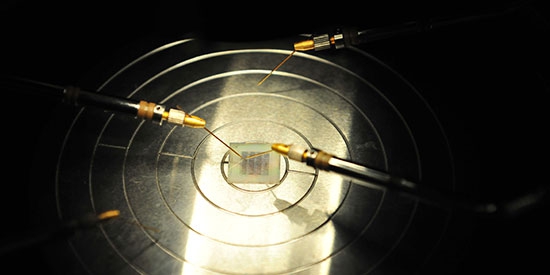

微电子学院实验室检测台

课题组成员在微电子实验室留影

北京时间2013年8月9日出版的最新一期《科学》杂志(Science)刊发了复旦大学微电子学院张卫团队最新科研论文,该团队提出并实现了一种新型的微电子基础器件:半浮栅晶体管(SFGT,Semi-Floating-Gate Transistor)。这是我国科学家在该顶级学术期刊上发表的第一篇微电子器件领域的原创性成果。

据悉,当代集成电路科技的发展主要是基于摩尔定律,该定律是由英特尔公司创始人之一戈登·摩尔提出的:芯片上的晶体管特征尺寸在不断地缩小,使得芯片上的晶体管数量每隔18个月便会增加一倍。

目前,集成电路的量产技术已发展到了22纳米技术节点,尽管我国在自主知识产权集成电路技术上取得了长足进步,但集成电路的核心技术基本上依然由国外公司拥有。我国集成电路产业主要依靠引进和吸收国外成熟的技术,在微电子核心器件及集成工艺上缺乏核心技术。半浮栅晶体管(SFGT)作为一种新型的微电子基础器件,它的成功研制将有助于我国掌握集成电路的核心技术,从而在芯片设计与制造上逐渐获得更多话语权。

半浮栅晶体管(SFGT):结构巧 性能高

金属-氧化物-半导体场效应晶体管(MOSFET)是目前集成电路中最基本的器件,工艺的进步让MOSFET晶体管的尺寸不断缩小,而其功率密度也一直在升高。我们常用的U盘等闪存芯片则采用了另一种称为浮栅晶体管的器件。闪存又称“非挥发性存储器”。所谓“非挥发”,就是在芯片没有供电的情况下,信息仍被保存不会丢失。这种器件在写入和擦除时都需要有电流通过一层接近5纳米厚的氧化硅介质,因此需要较高的操作电压(接近20伏)和较长的时间(微秒级)。复旦大学的科学家们把一个隧穿场效应晶体管(TFET)和浮栅器件结合起来,构成了一种全新的“半浮栅”结构的器件,称为半浮栅晶体管。

“硅基TFET晶体管使用了硅体内的量子隧穿效应,而传统的浮栅晶体管的擦写操作则是使电子隧穿过绝缘介质。”论文第一作者王鹏飞教授解释说。“隧穿”是量子世界的常见现象,可以“魔术般”地通过固体,好像拥有了穿墙术。“隧穿”势垒越低,相当于“墙”就越薄,器件隧穿所需电压也就越低。把TFET和浮栅相结合,半浮栅晶体管(SFGT)的“数据”擦写更加容易、迅速。“TFET为浮栅充放电、完成‘数据擦写’的操作,‘半浮栅’则实现“数据存放和读出”的功能。”张卫解释说,传统浮栅晶体管是将电子隧穿过高势垒(禁带宽度接近8.9 eV)的二氧化硅绝缘介质,而半浮栅晶体管(SFGT)的隧穿发生在禁带宽度仅1.1 eV的硅材料内,隧穿势垒大为降低。打个比方,原来在浮栅晶体管中,电子需要穿过的是一堵“钢筋水泥墙”,而在半浮栅晶体管中只需要穿过“木板墙”,“穿墙”的难度和所需的电压得以大幅降低,而速度则明显提升。这种结构设计可以让半浮栅晶体管的数据擦写更加容易、迅速,整个过程都可以在低电压条件下完成,为实现芯片低功耗运行创造了条件。

新型晶体管可在三大领域应用 拥有巨大的潜在市场

作为一种新型的基础器件,半浮栅晶体管(SFGT)可应用于不同的集成电路。首先,它可以取代一部分的SRAM,即静态随机存储器。SRAM是一种具有高速静态存取功能的存储器,多应用于中央处理器(CPU)内的高速缓存,对处理器性能起到决定性的作用。传统SRAM需用6个MOSFET晶体管才能构成一个存储单元,集成度较低,占用面积大。半浮栅晶体管则可以单个晶体管构成一个存储单元,存储速度接近由6个晶体管构成的SRAM存储单元。因此,由半浮栅晶体管(SFGT)构成的SRAM单元面积更小,密度相比传统SRAM大约可提高10倍。显然如果在同等工艺尺寸下,半浮栅晶体管(SFGT)构成的SRAM具有高密度和低功耗的明显优势。

其次,半浮栅晶体管(SFGT)还可以应用于DRAM领域。DRAM(Dynamic Random Access Memory),即动态随机存储器,广泛应用于计算机内存。其基本单元由1T1C构成,也就是一个晶体管加一个电容的结构。由于其电容需要保持一定电荷量来有效地存储信息,无法像MOSFET那样持续缩小尺寸。业界通常通过挖“深槽”等手段制造特殊结构的电容来缩小其占用的面积,但随着存储密度提升,电容加工的技术难度和成本大幅度提高。因此,业界一直在寻找可以用于制造DRAM的无电容器件技术,而半浮栅晶体管(SFGT)构成的DRAM无需电容器便可实现传统DRAM全部功能,不但成本大幅降低,而且集成度更高,读写速度更快。

半浮栅晶体管(SFGT)不但应用于存储器,它还可以应用于主动式图像传感器芯片(APS)。传统的图像传感器芯片需要用三个晶体管和一个感光二极管构成一个感光单元,而由单个半浮栅晶体管构成的新型图像传感器单元在面积上能缩小20%以上。感光单元密度提高,使图像传感器芯片的分辨率和灵敏度得到提升。

目前,DRAM、SRAM和图像传感器技术的核心专利基本上都是被美光、三星、Intel、索尼等国外公司控制。“在这些领域,中国大陆具有自主知识产权且可应用的产品几乎没有。”张卫教授说。半浮栅晶体管作为一种基础电子器件,它在存储和图像传感等领域的潜在应用市场规模达到三百亿美元以上。它的成功研制有助于我国掌握集成电路的核心器件技术,是我国在新型微电子器件技术研发上的一个里程碑。

制造工艺兼容度高 以产业化为最终目标

不同于实验室研究的基于碳纳米管、石墨烯等新材料的晶体管,半浮栅晶体管(SFGT)是一种基于标准硅CMOS工艺的微电子器件。SFGT原型器件首先在复旦大学的实验室中研制成功,而与标准CMOS工艺兼容的SFGT器件也已在国内生产线上成功制造出来。

“半浮栅晶体管(SFGT)兼容现有主流硅集成电路制造工艺,具有很好的产业化基础。”张卫教授表示半浮栅晶体管(SFGT)并不需要对现有集成电路制造工艺进行很大的改动。不过,新型器件往往还需要经过深入研究、性能优化、电路设计等大量的工作才能逐步实现产业化。目前针对这个器件的优化和电路设计工作也已经开始。

过去,国外集成电路厂商常会以高价将落后一到两代的技术淘汰给中国企业。“国外公司在市场上推出65纳米芯片后,便把90纳米芯片制造工艺卖给中国企业。”这是王鹏飞教授在国外从事65纳米技术研发的亲身经历。中国曾经有DRAM制造企业,由于与先进工艺存在一代半以上的技术差距而缺乏市场竞争力,现在已经不再做DRAM产品。“目前,我们国家的集成电路技术上跟国际领先水平还有不小的距离。”张卫教授表示。而技术基础薄弱、投入较少以及高端人才缺乏是其主要原因。半浮栅晶体管的发明及产业化推广,实际上是通过新型基础器件的技术优势来弥补我国IC企业在核心技术上的差距。如果将新器件技术转化为生产力,中国集成电路企业可以在某些应用领域大幅减少对国外技术的依赖,并形成具有极强竞争力的自主核心技术。

对于一项新的技术发明,我们还需要不断完善和夯实基础,这需要政府和相关部门的大力支持。另外,产业化的推广还要加强产学研的紧密合作。“我们希望能够有设计和制造伙伴与我们进行对接,向产业化推进。”张卫表示。设计公司出产品、制造企业生产、复旦大学提供技术支持,只有三方紧密合作才能实现半浮栅晶体管(SFGT)技术的产业化。

技术领先并不等于占领未来的广阔市场 后续研究仍需重视

拥有核心专利并不等于拥有未来的广阔市场。尽管半浮栅晶体管应用市场广阔,但前提是核心专利的优化布局。“我们要布局做得更快一点,避免被国外的大公司很快地赶超。”国外大公司拥有资金和人才优势,可以大规模申请专利,与之对比,张卫教授团队明显“势单力薄”。

张卫教授表示,目前的半浮栅晶体管(SFGT)是在较大工艺技术节点上实现的,主要是为了验证器件性能。未来研究工作主要集中于器件性能的优化和进一步提升,相关应用的电路设计和关键IP技术,以及技术节点缩小带来的一系列工艺问题等。

附:

复旦大学微电子学院及团队介绍

复旦大学微电子学院(简称学院)成立于2013年4月,是由原“微电子研究院”、“信息学院微电子学系”和“985微纳电子科技创新平台”合并而成,也是复旦大学积极响应“国家急需,世界一流”号召,发展工科“先行先试”的首个改革试点单位,是直属于学校的教学科研实体单位。学院拥有的“微电子学与固体电子学”学科,其前身是1958年由谢希德教授创办的半导体物理专业。在各级政府和复旦大学的大力支持下,微电子学院已拥有一个可以加工10纳米线宽的先进微纳电子器件研发平台。

张卫教授领导的团队长期以来一直从事集成电路工艺和新型半导体器件的研发。该团队是由张卫教授依托复旦大学微电子学科,历时多年逐步建立起来的。团队研究骨干为了共同的研究兴趣和目标,从世界各地陆续加入复旦大学。该团队近5年来的多项研究成果已发表于Science、IEEE Electron Device Letters、IEEE Transactions on Electron Devices、Applied Physics Letters等本领域顶级国际期刊上,并已获得中国及美国专利授权30余项。团队中有多位成员具有在国外微电子工业界第一线进行器件创新、工艺研发和技术转让的成功经验。本论文第一作者王鹏飞教授2003年在慕尼黑工业大学获得工学博士学位(Summa Cum Laude),之后加入德国英飞凌科技有限公司从事新器件研发工作,2009年6月加入复旦大学。